# **EDB7312 Development Kit**

# Hardware User's Manual

Embedded Processors Division

Copyright © 2001 - Cirrus Logic Inc. All rights reserved.

The information contained in this document is subject to change without notice.

# **Table of Contents**

| 1 Warranty                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1                                                                                                                          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| 2 Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2                                                                                                                          |

| 3 On-Board I/O Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3                                                                                                                          |

| 3.1 EDB7312 Address Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 3                                                                                                                          |

| 3.2 16 Mbyte STRATAFLASH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4                                                                                                                          |

| 3.3 8 Mbyte NAND FLASH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4                                                                                                                          |

| 3.4 Smart Media Socket                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4                                                                                                                          |

| 3.5 CS8900A Ethernet Controller with 1 Kbit EEPROM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 5                                                                                                                          |

| 3.6 Bi-Directional Parallel Port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 6                                                                                                                          |

| 3.7 Keyboard Extended Row Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                            |

| 3.8 USB Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 7                                                                                                                          |

| 3.9 PS/2 Keyboard/Mouse Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 7                                                                                                                          |

| 3.10 16-Bit IDE Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 8                                                                                                                          |

| 3.11 16 Mbyte SDRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 9                                                                                                                          |

| 3.12 CS53L32, 24-Bit Stereo A/D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                            |

| 3.13 CS43L42, 24-Bit Stereo D/A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 9                                                                                                                          |

| 4 EP73XX On-Chip I/O Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                            |

| 4.1 Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                            |

| 4.2 EP73xx Chip Selects                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                            |

| 4.3 EP73xx I/O Port Pin Assignments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 10                                                                                                                         |

| 4.4 EP73xx Interrupt Pin Assignments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 12                                                                                                                         |

| 4.5 EP73xx LCD Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 12                                                                                                                         |

| 4.6 EP73xx Digital Audio Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 13                                                                                                                         |

| 4.7 EP73xx Synchronous Serial Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                            |

| 4.8 EP73xx UARTS and Infrared I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 14                                                                                                                         |

| 4.9 EP73xx Reset and Mode Control Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 15                                                                                                                         |

| 5 EP73xx Initialization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                            |

| 5.1 Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                            |

| 5.2 Ports A-E Direction Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                            |

| 5.3 SYSCON Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                            |

| 5.4 Interrupt Mask Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                            |

| 5.5 Memory Configuration Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 17                                                                                                                         |

| 5.6 SDRAM Configuration Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 18                                                                                                                         |

| 5.7 LCD Controller Registers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 19                                                                                                                         |

| 6 Connectors, LEDs and Pots                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 21                                                                                                                         |

| 6.1 Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 21                                                                                                                         |

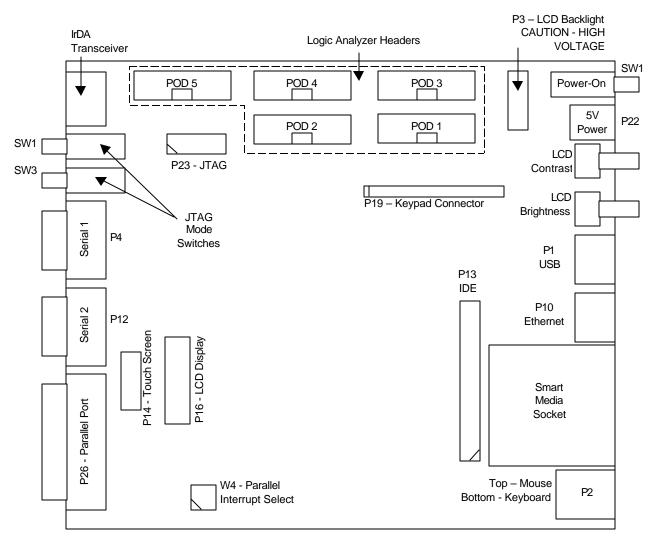

| 6.2 Connector, Jumper and Header Locations – Top Side                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 21                                                                                                                         |

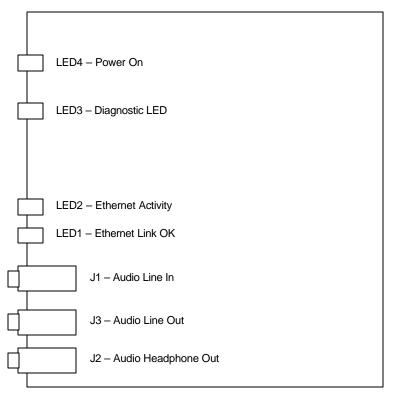

| 6.3 Connector and LED Locations – Bottom Side                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 22                                                                                                                         |

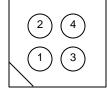

| 6.4 W4, Parallel Port Interrupt Select                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                            |

| 6.5 P1, USB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                            |

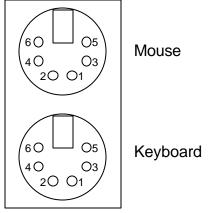

| 6.6 P2, Dual Mini-DIN Connector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                            |

| 6.7 P4 and P12, DB-9 Male Serial Connectors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 24                                                                                                                         |

| 6.8 P10, RJ45 Connector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 25                                                                                                                         |

| 6.8 P10, RJ45 Connector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 25<br>25                                                                                                                   |

| 6.8 P10, RJ45 Connector<br>6.9 P13, IDE Connector<br>6.10 P22, 2.1 mm Power Jack                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 25<br>25<br>26                                                                                                             |

| 6.8 P10, RJ45 Connector<br>6.9 P13, IDE Connector<br>6.10 P22, 2.1 mm Power Jack<br>6.11 P23, 14-Pin JTAG Header                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 25<br>25<br>26<br>26                                                                                                       |

| 6.8 P10, RJ45 Connector<br>6.9 P13, IDE Connector<br>6.10 P22, 2.1 mm Power Jack<br>6.11 P23, 14-Pin JTAG Header<br>6.12 P26, DB-25 Parallel I/O Connector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 25<br>25<br>26<br>26<br>26                                                                                                 |

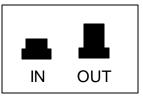

| 6.8 P10, RJ45 Connector<br>6.9 P13, IDE Connector<br>6.10 P22, 2.1 mm Power Jack<br>6.11 P23, 14-Pin JTAG Header<br>6.12 P26, DB-25 Parallel I/O Connector<br>6.13 J1, J2 and J3, Audio Jacks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 25<br>25<br>26<br>26<br>26<br>27                                                                                           |

| 6.8 P10, RJ45 Connector         6.9 P13, IDE Connector         6.10 P22, 2.1 mm Power Jack         6.11 P23, 14-Pin JTAG Header         6.12 P26, DB-25 Parallel I/O Connector         6.13 J1, J2 and J3, Audio Jacks         6.14 LED Displays                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 25<br>25<br>26<br>26<br>26<br>27<br>27                                                                                     |

| <ul> <li>6.8 P10, RJ45 Connector</li> <li>6.9 P13, IDE Connector</li> <li>6.10 P22, 2.1 mm Power Jack</li> <li>6.11 P23, 14-Pin JTAG Header</li> <li>6.12 P26, DB-25 Parallel I/O Connector</li> <li>6.13 J1, J2 and J3, Audio Jacks</li> <li>6.14 LED Displays</li> <li>6.15 RP1, LCD Brightness and RP2, LCD Conrtast Adjust</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                          | 25<br>26<br>26<br>26<br>26<br>27<br>27<br>28                                                                               |

| <ul> <li>6.8 P10, RJ45 Connector.</li> <li>6.9 P13, IDE Connector.</li> <li>6.10 P22, 2.1 mm Power Jack.</li> <li>6.11 P23, 14-Pin JTAG Header</li> <li>6.12 P26, DB-25 Parallel I/O Connector.</li> <li>6.13 J1, J2 and J3, Audio Jacks.</li> <li>6.14 LED Displays.</li> <li>6.15 RP1, LCD Brightness and RP2, LCD Conrtast Adjust.</li> <li>6.16 SW2, Power Switch.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                  | 25<br>26<br>26<br>26<br>26<br>27<br>27<br>28<br>28                                                                         |

| <ul> <li>6.8 P10, RJ45 Connector.</li> <li>6.9 P13, IDE Connector.</li> <li>6.10 P22, 2.1 mm Power Jack.</li> <li>6.11 P23, 14-Pin JTAG Header</li> <li>6.12 P26, DB-25 Parallel I/O Connector.</li> <li>6.13 J1, J2 and J3, Audio Jacks.</li> <li>6.14 LED Displays.</li> <li>6.15 RP1, LCD Brightness and RP2, LCD Conrtast Adjust.</li> <li>6.16 SW2, Power Switch.</li> <li>6.17 SW1 and SW3, JTAG Mode Select.</li> </ul>                                                                                                                                                                                                                                                                                                                     | 25<br>26<br>26<br>26<br>26<br>27<br>27<br>28<br>28<br>28                                                                   |

| 6.8 P10, RJ45 Connector         6.9 P13, IDE Connector.         6.10 P22, 2.1 mm Power Jack.         6.11 P23, 14-Pin JTAG Header         6.12 P26, DB-25 Parallel I/O Connector.         6.13 J1, J2 and J3, Audio Jacks.         6.14 LED Displays.         6.15 RP1, LCD Brightness and RP2, LCD Conrtast Adjust.         6.16 SW2, Power Switch.         6.17 SW1 and SW3, JTAG Mode Select.         7 Macraigor "Wiggler".                                                                                                                                                                                                                                                                                                                    | 25<br>25<br>26<br>26<br>26<br>27<br>27<br>27<br>28<br>28<br>28<br>29                                                       |

| 6.8 P10, RJ45 Connector         6.9 P13, IDE Connector.         6.10 P22, 2.1 mm Power Jack.         6.11 P23, 14-Pin JTAG Header         6.12 P26, DB-25 Parallel I/O Connector.         6.13 J1, J2 and J3, Audio Jacks.         6.14 LED Displays.         6.15 RP1, LCD Brightness and RP2, LCD Conrtast Adjust.         6.16 SW2, Power Switch.         6.17 SW1 and SW3, JTAG Mode Select.         7 Macraigor "Wiggler".         7.1 Overview                                                                                                                                                                                                                                                                                               | 25<br>25<br>26<br>26<br>26<br>27<br>27<br>27<br>28<br>28<br>28<br>29<br>29                                                 |

| 6.8 P10, RJ45 Connector         6.9 P13, IDE Connector.         6.10 P22, 2.1 mm Power Jack.         6.11 P23, 14-Pin JTAG Header         6.12 P26, DB-25 Parallel I/O Connector.         6.13 J1, J2 and J3, Audio Jacks.         6.14 LED Displays.         6.15 RP1, LCD Brightness and RP2, LCD Conrtast Adjust.         6.16 SW2, Power Switch.         6.17 SW1 and SW3, JTAG Mode Select.         7 Macraigor "Wiggler".         7.1 Overview         7.2 Wiggler Connection                                                                                                                                                                                                                                                                | 25<br>25<br>26<br>26<br>26<br>27<br>27<br>27<br>28<br>28<br>28<br>28<br>29<br>29<br>29                                     |

| 6.8 P10, RJ45 Connector         6.9 P13, IDE Connector.         6.10 P22, 2.1 mm Power Jack.         6.11 P23, 14-Pin JTAG Header         6.12 P26, DB-25 Parallel I/O Connector.         6.13 J1, J2 and J3, Audio Jacks.         6.14 LED Displays.         6.15 RP1, LCD Brightness and RP2, LCD Conrtast Adjust.         6.16 SW2, Power Switch.         6.17 SW1 and SW3, JTAG Mode Select.         7 Macraigor "Wiggler".         7.1 Overview         7.2 Wiggler Connection         8 Software Migration                                                                                                                                                                                                                                   | 25<br>26<br>26<br>26<br>26<br>27<br>27<br>27<br>28<br>28<br>28<br>29<br>29<br>29<br>29<br>30                               |

| 6.8 P10, RJ45 Connector         6.9 P13, IDE Connector         6.10 P22, 2.1 mm Power Jack.         6.11 P23, 14-Pin JTAG Header         6.12 P26, DB-25 Parallel I/O Connector.         6.13 J1, J2 and J3, Audio Jacks         6.14 LED Displays.         6.15 RP1, LCD Brightness and RP2, LCD Conrtast Adjust.         6.16 SW2, Power Switch.         6.17 SW1 and SW3, JTAG Mode Select.         7 Macraigor "Wiggler".         7.1 Overview         7.2 Wiggler Connection         8 Software Migration         8.1 Introduction                                                                                                                                                                                                            | 25<br>25<br>26<br>26<br>26<br>27<br>27<br>27<br>28<br>28<br>28<br>28<br>29<br>29<br>29<br>29<br>30<br>30                   |

| 6.8 P10, RJ45 Connector         6.9 P13, IDE Connector         6.10 P22, 2.1 mm Power Jack.         6.11 P23, 14-Pin JTAG Header         6.12 P26, DB-25 Parallel I/O Connector.         6.13 J1, J2 and J3, Audio Jacks.         6.14 LED Displays.         6.15 RP1, LCD Brightness and RP2, LCD Conrtast Adjust.         6.16 SW2, Power Switch.         6.17 SW1 and SW3, JTAG Mode Select.         7 Macraigor "Wiggler"         7.1 Overview         7.2 Wiggler Connection         8 Software Migration         8.1 Introduction         8.2 Boot-up Code                                                                                                                                                                                   | 25<br>25<br>26<br>26<br>26<br>27<br>27<br>27<br>28<br>28<br>28<br>28<br>29<br>29<br>29<br>29<br>29<br>30<br>30<br>30       |

| 6.8 P10, RJ45 Connector         6.9 P13, IDE Connector         6.10 P22, 2.1 mm Power Jack.         6.11 P23, 14-Pin JTAG Header         6.12 P26, DB-25 Parallel I/O Connector.         6.13 J1, J2 and J3, Audio Jacks.         6.14 LED Displays.         6.15 RP1, LCD Brightness and RP2, LCD Conrtast Adjust.         6.16 SW2, Power Switch.         6.17 SW1 and SW3, JTAG Mode Select.         7 Macraigor "Wiggler"         7.1 Overview         7.2 Wiggler Connection         8 Software Migration         8.1 Introduction.         8.2 Boot-up Code         8.2.1 Clock Mode and Rate                                                                                                                                                | 25<br>25<br>26<br>26<br>26<br>27<br>27<br>28<br>28<br>28<br>28<br>29<br>29<br>29<br>29<br>30<br>30<br>30                   |

| 6.8 P10, RJ45 Connector.         6.9 P13, IDE Connector.         6.10 P22, 2.1 mm Power Jack.         6.11 P23, 14-Pin JTAG Header         6.12 P26, DB-25 Parallel I/O Connector.         6.13 J1, J2 and J3, Audio Jacks.         6.14 LED Displays.         6.15 RP1, LCD Brightness and RP2, LCD Contrast Adjust.         6.16 SW2, Power Switch.         6.17 SW1 and SW3, JTAG Mode Select.         7 Macraigor "Wiggler"         7.1 Overview         7.2 Wiggler Connection                                                                                                                                                                                                                                                                | 25<br>25<br>26<br>26<br>26<br>27<br>27<br>28<br>28<br>28<br>28<br>28<br>29<br>29<br>29<br>30<br>30<br>30<br>30             |

| 6.8 P10, RJ45 Connector         6.9 P13, IDE Connector.         6.10 P22, 2.1 mm Power Jack.         6.11 P23, 14-Pin JTAG Header         6.12 P26, DB-25 Parallel I/O Connector.         6.13 J1, J2 and J3, Audio Jacks.         6.14 LED Displays.         6.15 RP1, LCD Brightness and RP2, LCD Conrtast Adjust.         6.16 SW2, Power Switch.         6.17 SW1 and SW3, JTAG Mode Select.         7 Macraigor "Wiggler".         7.1 Overview         7.2 Wiggler Connection         8 Software Migration         8.1 Introduction.         8.2 Boot-up Code         8.2.1 Clock Mode and Rate         8.2.2 CS0 size and Speed         8.2.3 CS1 NAND FLASH.                                                                               | 25<br>25<br>26<br>26<br>26<br>27<br>27<br>27<br>28<br>28<br>28<br>28<br>29<br>29<br>29<br>29<br>30<br>30<br>30<br>30       |

| 6.8 P10, RJ45 Connector         6.9 P13, IDE Connector.         6.10 P22, 2.1 mm Power Jack.         6.11 P23, 14-Pin JTAG Header         6.12 P26, DB-25 Parallel I/O Connector.         6.13 J1, J2 and J3, Audio Jacks.         6.14 LED Displays.         6.15 RP1, LCD Brightness and RP2, LCD Conrtast Adjust.         6.16 SW2, Power Switch.         6.17 SW1 and SW3, JTAG Mode Select.         7 Macraigor "Wiggler".         7.1 Overview         7.2 Wiggler Connection.         8 Software Migration.         8.1 Introduction.         8.2 Boot-up Code         8.2.1 Clock Mode and Rate.         8.2.2 CS0 size and Speed.         8.2.3 CS1 NAND FLASH.                                                                           | 25<br>25<br>26<br>26<br>26<br>27<br>27<br>28<br>28<br>28<br>28<br>29<br>29<br>29<br>29<br>30<br>30<br>30<br>30<br>30<br>31 |

| 6.8 P10, RJ45 Connector         6.9 P13, IDE Connector.         6.10 P22, 2.1 mm Power Jack.         6.11 P23, 14-Pin JTAG Header         6.12 P26, DB-25 Parallel I/O Connector         6.13 J1, J2 and J3, Audio Jacks.         6.14 LED Displays.         6.15 RP1, LCD Brightness and RP2, LCD Conrtast Adjust.         6.16 SW2, Power Switch.         6.17 SW1 and SW3, JTAG Mode Select.         7 Macraigor "Wiggler".         7.1 Overview         7.2 Wiggler Connection         8 Software Migration         8.1 Introduction.         8.2 Boot-up Code         8.2.1 Clock Mode and Rate.         8.2.2 CS0 size and Speed.         8.2.3 CS1 NAND FLASH.         8.3 LCD Controller         8.4 Touch Screen Interface.               | 25<br>25<br>26<br>26<br>27<br>27<br>28<br>28<br>28<br>29<br>29<br>29<br>29<br>29<br>30<br>30<br>30<br>30<br>31<br>31       |

| 6.8 P10, RJ45 Connector         6.9 P13, IDE Connector         6.10 P22, 2.1 mm Power Jack         6.11 P23, 14-Pin JTAG Header         6.12 P26, DB-25 Parallel I/O Connector         6.13 J1, J2 and J3, Audio Jacks         6.14 LED Displays         6.15 RP1, LCD Brightness and RP2, LCD Contrast Adjust         6.16 SW2, Power Switch         6.17 SW1 and SW3, JTAG Mode Select         7 Macraigor "Wiggler"         7.1 Overview         7.2 Wiggler Connection         8 Software Migration         8.1 Introduction         8.2 Boot-up Code         8.2.1 Clock Mode and Rate         8.2.2 CS0 size and Speed         8.2.3 CS1 NAND FLASH.         8.3 LCD Controller         8.4 Touch Screen Interface         8.5 IDE Interface | 25<br>25<br>26<br>26<br>27<br>27<br>27<br>28<br>28<br>29<br>29<br>29<br>29<br>29<br>30<br>30<br>30<br>30<br>31<br>31<br>31 |

| 6.8 P10, RJ45 Connector         6.9 P13, IDE Connector.         6.10 P22, 2.1 mm Power Jack.         6.11 P23, 14-Pin JTAG Header         6.12 P26, DB-25 Parallel I/O Connector         6.13 J1, J2 and J3, Audio Jacks.         6.14 LED Displays.         6.15 RP1, LCD Brightness and RP2, LCD Conrtast Adjust.         6.16 SW2, Power Switch.         6.17 SW1 and SW3, JTAG Mode Select.         7 Macraigor "Wiggler".         7.1 Overview         7.2 Wiggler Connection         8 Software Migration         8.1 Introduction.         8.2 Boot-up Code         8.2.1 Clock Mode and Rate.         8.2.2 CS0 size and Speed.         8.2.3 CS1 NAND FLASH.         8.3 LCD Controller         8.4 Touch Screen Interface.               | 25<br>25<br>26<br>26<br>27<br>27<br>27<br>28<br>28<br>29<br>29<br>29<br>29<br>29<br>30<br>30<br>30<br>30<br>31<br>31<br>31 |

# List of Tables

| Table 1 – EDB7312 Address Map                                   | 3    |

|-----------------------------------------------------------------|------|

| Table 2 – NAND FLASH Signal Assignments                         |      |

| Table 3 – CS8900A Address Map                                   | 5    |

| Table 4 – Parallel Port Control/Status Register Bit Assignments | 6    |

| Table 5 – PDIUSBD12 Address Map                                 |      |

| Table 6 – 8042 PS/2 Keyboard/Mouse Controller Address Map       | 8    |

| Table 7 – 16-Bit IDE Interface Address Map                      |      |

| Table 8 – EP73xx Chip Select Assignments                        |      |

| Table 9 – EP73xx Port Pin Assignments                           |      |

| Table 10 – EP73xx Interrupt Pin Assignments                     |      |

| Table 11 – EP73xx to DMF-50944 LCD Signal Connections           |      |

| Table 12 – EP73xx Digital Audio Interface Pin Assignments       |      |

| Table 13 – EP73xx Synchronous Serial Interface Pin Assignments  |      |

| Table 14 – UART and Infrared Pin Assignments                    |      |

| Table 15 – EP73xx Reset and Mode Control Pin Assignments        |      |

| Table 16 – Port A-E Data Direction Register Default Values      |      |

| Table 17 – SYSCON1-3 Register Default Values                    |      |

| Table 18 – MEMCFG1-2 Register Default Values                    |      |

| Table 19 – SDRAM Configuration Registers Default Values         |      |

| Table 20 – LCD Configuration Registers Default Values           |      |

| Table 21 – Parallel Port Interrupt Source                       |      |

| Table 22 – P1, USB Connector Pinout                             |      |

| Table 23 – P6, Dual Mini-DIN Connector Pinout                   |      |

| Table 24 – P4 and P12, DB-9 Pinouts                             |      |

| Table 25 – P10, RJ45 Connector Pinout                           |      |

| Table 26 – P23, IDE Connector Pinout                            |      |

| Table 27 – P23, 14-Pin JTAG Header Pinout                       |      |

| Table 28 – P26, DB-25 Parallel I/O Connector Pinout             |      |

| Table 29 – LED Display Assignments                              |      |

| Table 30 – JTAG Debug Switch Settings                           | . 28 |

# **1 WARRANTY**

The enclosed product ("the Product"), a part of the Cogent Modular Architecture or Cogent Single Board series, is warranted by Cogent Computer Systems, Inc. ("Cogent") for a period of six months for reasonable development testing and use, all as further described and defined below. This warranty runs solely to the individual or entity purchasing the Product and is not transferable or assignable in any respect. This warranty is valid only for so long as the product is used intact as shipped from Cogent or Cirrus Logic, Inc. Any attempt or effort to alter the Product, including but not limited to any attempt to solder, desolder, unplug, replace, add or affix any part or component of or onto the Product, other than components specifically intended for the user to plug and unplug into appropriate sockets and/or connectors to facilitate user programming and development, all as specifically described and authorized in the Cogent Customer Product Users Manual, shall void this warranty in all respects. Coverage under this warranty requires that the Product be used and stored at all times in conditions with proper electrostatic protection necessary and appropriate for a complex electronic device. These conditions include proper temperature, humidity, radiation, atmosphere and voltage (standard electronics lab conditions). Any Product that has been modified without the express, prior written consent of Cogent is not covered by this warranty. Cogent Single Board and Cogent Modular Architecture test and bus connectors are for use with Cogent adapters only. The use or connection of any test or bus connector, adapter or component other than a Cogent connector or adapter shall void this warranty and the warranty of all other components, parts and modules connected to the rest of the system. Cogent shall not be responsible for any damage to the Product as a result of a customer's use or application of circuitry not developed or approved by Cogent for use on or in connection with the Product.

This warranty does not cover defects caused by electrical or temperature fluctuations or from stress resulting from or caused by abuse, misuse or misapplication of the Product. Any evidence of tampering with the serial number on the Product shall immediately void this warranty. This Product is not intended to be used on or embedded in or otherwise used in connection with any life sustaining or life saving product and this warranty is not applicable nor is Cogent liable in any respect if the Product is so used. Notwithstanding anything to the contrary herein, Cogent expressly disclaims any implied warranty of merchantability or implied warranty of fitness for a particular purpose in connection with the manufacture or use of the Product.

# 2 OVERVIEW

The EDB7312 (Cogent part number CSB238) was designed and developed by Cogent Computer Systems, Inc. for Cirrus Logic, Inc. as a highly Integrated EP73xx development platform. Based upon the Cirrus Logic, Inc. Maverick series of ARM processors, the EDB7312 provides a powerful, flexible platform for software design and development, hardware prototyping, embedded control systems, and more. The major features of the EDB7312 are:

- 74 MHz Cirrus Logic EP7312 Highly Integrated ARM Microprocessor

- Dual RS-232 Serial I/O

- Infrared Interface (115K baud)

- Integrated LCD Controller with interface to Optrex DMF-50944, 320x240 Color LCD Display

- 16 Mbyte SDRAM

- 16 Mbyte Intel E28F128 StrataFlash

- 8 Mbyte NAND FLASH

- Socket for 8-128Mbyte External Smart Media Card

- Bi-directional Parallel I/O Interface

- 16-Bit IDE Interface

- External Keypad Interface

- Intel 8042 PS/2 Keyboard/Mouse Controller

- Cirrus Logic CS8900A 10Mbit Ethernet Controller with 1 Kbyte EEPROM

- Burr-Brown AD7846 Touch Screen Controller

- Crystal CS53L32 24-Bit, CD Quality, Stereo Analog-Digital Converter

- Crystal CS43L42 24-Bit, CD Quality, Stereo Digital-Analog Converter with Integrated Headphone Amplifier

- Phillips Semiconductor PDIUSBD12 USB Peripheral Controller

- Built-in Macraigor "Wiggler" Interface for JTAG Based Debugging via the Parallel Port

# **3 ON-BOARD I/O DEVICES**

#### 3.1 EDB7312 ADDRESS MAP

The following table describes the Address Map of the EDB7312.

| EP73xx<br>Chip<br>Select | Chip<br>Select<br>Width <sup>6</sup> | Default<br>Wait<br>States <sup>6</sup> | Address<br>Start <sup>1, 2, 3</sup> | Address<br>End | Description                        |

|--------------------------|--------------------------------------|----------------------------------------|-------------------------------------|----------------|------------------------------------|

| CS0                      | 16                                   | 5                                      | 0x0000000                           | 0x00FFFFFF     | 16 Mbyte StrataFlash               |

| CS1                      | 8                                    | 2                                      | 0x1000000                           | 0x10000000     | On-Board NAND FLASH                |

|                          |                                      |                                        |                                     |                | and SmartMedia Socket <sup>5</sup> |

| CS2                      | 16                                   | 4                                      | 0x20000000                          | 0x200000F      | CS8900A Ethernet                   |

|                          |                                      |                                        |                                     |                | Controller                         |

| CS2                      | 16                                   | 4                                      | 0x20000300                          | 0x2000030F     | CS8900A PC-AT                      |

|                          |                                      |                                        |                                     |                | Compatibility Address              |

| CS3                      | 8                                    | 1                                      | 0x30000000                          | 0x30000001     | Parallel Interface Registers       |

| CS3                      | 8                                    | 1                                      | 0x30010000                          | 0x30010000     | Keyboard Extended Row              |

|                          |                                      |                                        |                                     |                | Register                           |

| CS4                      | 8                                    | 4                                      | 0x40000000                          | 0x400000F      | PDIUSBD12 USB                      |

|                          |                                      |                                        |                                     |                | Controller                         |

| CS4                      | 8                                    | 4                                      | 0x40010000                          | 0x40010001     | 8042 PS/2 Keyboard/Mouse           |

|                          |                                      |                                        |                                     |                | Controller                         |

| CS5                      | 8/16 <sup>7</sup>                    | 1                                      | 0x5000000                           | 0x5000006      | IDE Interface                      |

| CS6 <sup>8</sup>         | 32                                   | 0                                      | 0x6000000                           | 0x600095FF     | 48 KByte SRAM                      |

| $CS7^8$                  | 32                                   | 0                                      | 0x70000000                          | 0x7000007F     | Boot ROM                           |

| N/A                      | N/A                                  | 0                                      | 0x8000000                           | 0x80003FFF     | EP73xx Registers                   |

| SDCS                     | 32                                   | N/A                                    | 0xC0000000                          | 0xC0FFFFFF     | 16 Mbyte SDRAM                     |

#### Table 1 – EDB7312 Address Map

#### Address Map Notes:

- 1. All addresses shown are physical addresses in normal (non-Boot ROM) mode. Refer to the EP73xx documentation for a description of the Chip Select mapping for Boot ROM Mode.

- 2. The EP73xx MMU may be setup to create different virtual address maps. Refer to the appropriate software documentation for any deviations from this map.

- 3. All addresses not listed here are reserved.

- 4. Many devices do not fully map their entire allotted address space. However, for future compatibility, do not access the devices outside of their address ranges listed here.

- 5. The On-Board NAND FLASH and the Smart Media Socket occupy one byte of address space. Selection of the desired device is done via EP73xx Control lines. Refer to Section 3.3 for more information.

- 6. Chip Select Width and Wait states are recommended values. Refer to the appropriate software documentation for detailed information regarding these values. Failure to adhere to

these values, however, may cause erratic behavior of the hardware.

- 7. CS5 must be placed in 8-bit mode when accessing the IDE Command and Status Registers. It must be placed in 16-Bit mode when accessing the IDE Data Register.

- 8. CS6 and CS7 are internal only and are described here for completeness purposes only.

# 3.2 16 MBYTE STRATAFLASH

The EDB7312 uses the Intel E28F128J3-150 StrataFlash device for boot memory. This device is enabled as 8M x 16. CS0 must be set to 16-bits width (this is the default on reset) and 5 wait states (the default is 8 wait states after reset). Refer to the "Intel StrataFlash Memory", Document Number #290667-006 for detailed programming information.

# 3.3 8 MBYTE NAND FLASH

The CS238 provides 8 Mbytes of built-in NAND FLASH using the Toshiba TC58V64AFT device. Note that this may be changed in future revisions to a different, but compatible vendor. This device is controlled using a number of EP73xx signals, including programmed I/O Port signals. The following table details the signal connections between the TC58V64 and the EP73xx.

| TC58V64<br>Signal | EP73xx<br>Signal | Notes                                                                               |

|-------------------|------------------|-------------------------------------------------------------------------------------|

| nCE               | Port B Bit 6     | Clearing Bit 6 sets nCE low to the TC58V64.<br>Note that Port B Bit 7 must be high. |

| CLE               | Port B Bit 4     | Setting Bit 4 high, sets CLE high                                                   |

| ALE               | Port B Bit 5     | Setting Bit 4 high, sets ALE high                                                   |

| nRE               | nOE & CS1        | nRE goes low when nOE and CS1 are both true                                         |

| nWE               | nMWE & CS1       | nWE goes low when nMWE and CS1 are both true                                        |

#### Table 2 – NAND FLASH Signal Assignments

Refer to the Toshiba TC58V64AFT Data Sheet for detailed programming information.

# 3.4 SMART MEDIA SOCKET

The EDB7312 allows the user to add additional NAND FLASH storage via the Smart Media Socket. This socket can accommodate any industry standard Smart Media (also known as SSFDC) card. Current cards provide from 8 Mbytes to 128 Mbytes of storage. The Smart Media Socket uses the same set of control signals as the on-board NAND FLASH with the exception that nCE to the Smart Media Socket goes low when Port B Bit 7 is low and Port B Bit 6 is high.

#### 3.5 CS8900A ETHERNET CONTROLLER WITH 1 KBIT EEPROM

The CS8900A is used to provide the EDB7312 with a 10 Mbit Ethernet interface. The address map of the CS8900A is shown in the following table.

| Address    | Write Description                                                   | Read Description                                                      |

|------------|---------------------------------------------------------------------|-----------------------------------------------------------------------|

| 0x20000000 | Transmit Data, Port 0                                               | Receive Data, Port 0                                                  |

| 0x20000002 | Transmit Data, Port 1 -<br>32-Bit Mode only, <b>Do Not Use</b>      | Receive Data, Port 1 -<br>32-Bit Mode only, <b>Do Not Use</b>         |

| 0x20000004 | Transmit Command                                                    | N/A                                                                   |

| 0x20000006 | Transmit Length                                                     | N/A                                                                   |

| 0x20000008 | N/A                                                                 | Interrupt Status Queue                                                |

| 0x2000000A | Write Packet Page Pointer                                           | Read Packet Page Pointer                                              |

| 0x2000000C | Write Packet Page Data Port 0                                       | Read Packet Page Data, Port 0                                         |

| 0x2000000E | Write Packet Page Data Port 1 – 32-Bit Mode only, <b>Do Not Use</b> | Read Packet Page Data Port 1 –<br>32-Bit Mode only, <b>Do Not Use</b> |

Table 3 – CS8900A Address Map

CS8900A Notes:

- 1. A 1 kbit EEPROM is attached to the CS8900A allowing for Non-Volatile storage for system parameters such as Ethernet MAC Address, routing tables, etc. Refer to the CS8900A Data Sheet for detailed information on accessing and programming the EEPROM.

- Address lines SA8 and SA9 of the CS8900A are tied high, while SA4-SA7 and SA10-SA19 are all tied low. This causes the CS8900A to see addresses 0x00300 to 0x0030F only. This provides compatibility for software designed to work in a PC-AT ISA bus environment. Software may access the CS8900A at the EP73xx 0x20000300 base address or at 0x20000000.

- 3. CS8900A Interrupt output 0 is used to signal an interrupt to the EP73xx. This interrupt is routed to EINT3, which is shared with the Parallel Port. Software must setup CS8900A Interrupt 0 as level, high true.

- 4. Two LED's are provided to indicate the status of the Ethernet link. They are "Activity" and "Link". Refer to Section 6.3 for the location of these displays.

#### 3.6 BI-DIRECTIONAL PARALLEL PORT

Implemented in logic is a simple bi-directional parallel port interface. This interface is fully software controlled and provides no additional support for various parallel port transfer modes. This interface consists of two 8-bit registers. The first, located at 0x30000000 is used to read/write the 8-data parallel port data bits. The second, at location 0x30000001 allows software to read/write the control/status signals as well as control the direction of the data register. The control/status register bit assignments are shown in the following table.

| Bit | Write Description                                                                         | Read Description             |

|-----|-------------------------------------------------------------------------------------------|------------------------------|

| 0   | Set nPERROR Pin                                                                           | Read state of nPERROR<br>Pin |

| 1   | Set PE Pin                                                                                | Read state of PE Pin         |

| 2   | Set nACK Pin                                                                              | Read state of nACK Pin       |

| 3   | Set BUSY Pin                                                                              | Read state of BUSY Pin       |

| 4   | 0 = Set Data Register Direction to<br>Read<br>1 = Set Data Register Direction to<br>Write | Read state of nSTROBE<br>Pin |

| 5   | Set SLCT Pin                                                                              | Read state of nAFD Pin       |

| 6   | 0 = Disable Parallel Port Interrupt                                                       | Read state of nSLCTIN Pin    |

|     | 1 = Enable Parallel Port Interrupt                                                        |                              |

| 7   | Unused, must be 0                                                                         | Read state of INIT Pin       |

Table 4 – Parallel Port Control/Status Register Bit Assignments

Parallel Port Notes:

- For compatibility purposes, software may read/write the data and control registers using a single 32-bit read/write. As long as CS3 is setup correctly for 8bits, the EP73xx will perform four 8-bit transfers. Newer software should do individual 8-bit reads/writes, as this will be a bit quicker since only two of the bytes are valid.

- An option jumper is used to allow the Parallel Port to generate an interrupt to the EP73xx. One of four signals (nACK, nSTROBE, nSLCTIN or nINIT) may be selected, and when that selected signal is low, EINT3 (which is shared with the CS8900A Ethernet Controller) will be driven high. Refer to section 6.4 for detailed information regarding this jumper.

# 3.7 KEYBOARD EXTENDED ROW REGISTER

The Matrix Keyboard controller on the EP73xx provides 8 column bits and 8 row bits (Port A) thus allowing a maximum of 64 keys. In order to support larger arrays, an additional 8-bit register is provided to read another 8 rows, thus extending the maximum array size to 128 keys. Note that these rows cannot however, generate an interrupt as is possible with the Port A inputs. This register is located at 0x30010000.

#### 3.8 USB CONTROLLER

The EDB7312 uses the PDIUSBD12 to provide a peripheral USB connection. The PDIUSBD12 supports all protocols as defined by the USB Standard, version 1.1. Software communicates with the PDISUBD12 via two 8-bit registers as shown in the following table.

| Address    | Write Description     | Read Description |

|------------|-----------------------|------------------|

| 0x40000000 | Write Data            | Read Data        |

| 0x40000001 | Write Command/Address | Read Status      |

Table 5 – PDIUSBD12 Address Map

PDIUSBD12 Notes:

- 1. The PDIUSBD12 Suspend status signal is routed to the EP73xx Port E Bit 1 input. When the PDIUSBD12 is in the suspend state, this bit will be 1.

- 2. The PDISUBD12 Interrupt output is routed to the EP73xx nEINT1 input. Note that this interrupt is shared with the 8042 PS/2 Keyboard/Mouse Controller.